SolVisionFallstudie

Erkennung von Abplatzfehlern beim Wafer-Dicing

Qualitätskontrolle von Halbleiter-Dies mit KI

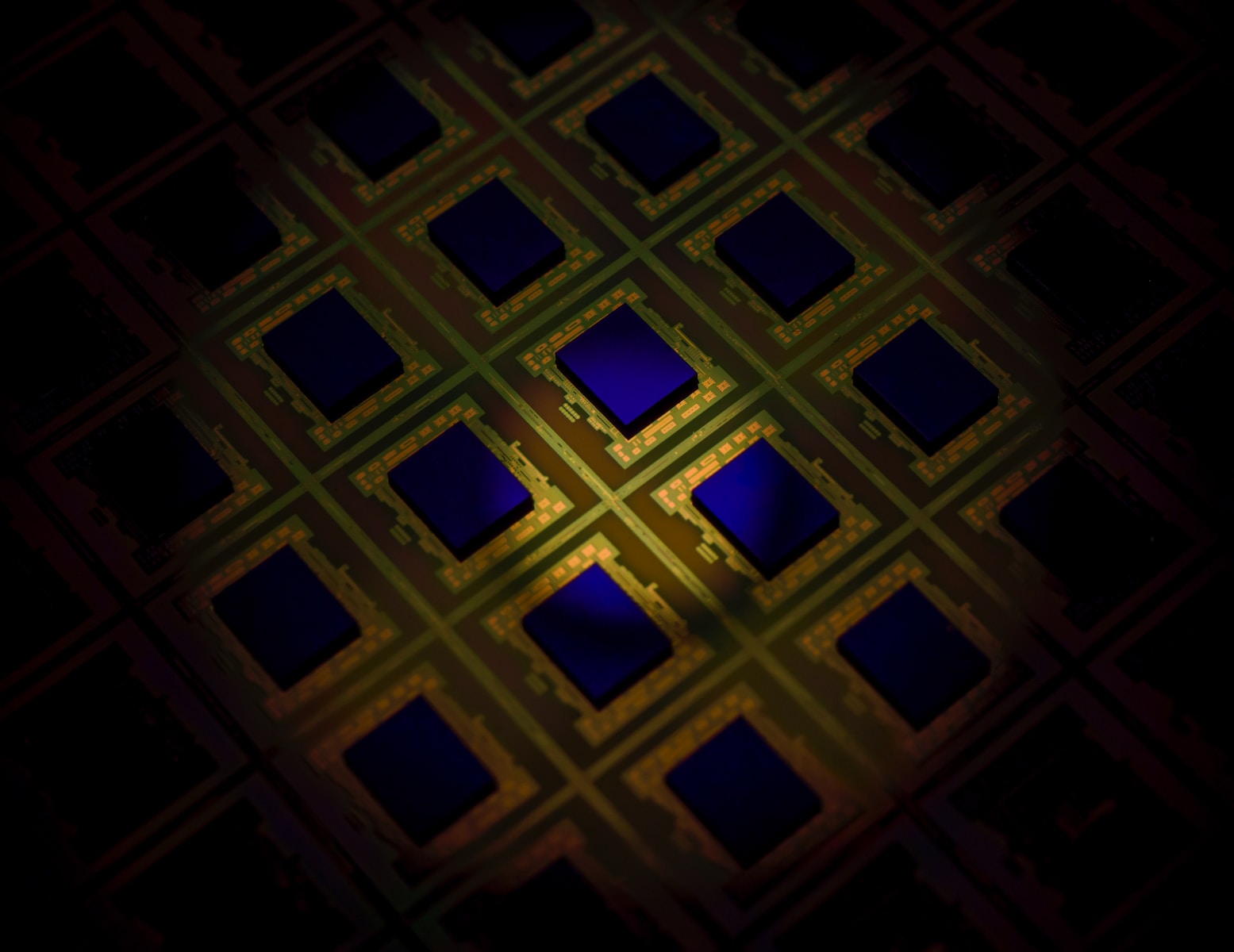

Reduzierung der Halbleiter-Wafergröße

Das Wafer-Sägen hilft, den Wafer in einzelne Dies für die anschließende Verarbeitung zu trennen. Da moderne Elektronik dünnere, kleinere und leichtere Wafer benötigt, erfordert das Verkleinern von Wafer-Chips genauere Schneidprozesse. Die Schneidwege werden verengt, die Siliziumkristalle werden fragiler, und schneidungsbedingte Schäden sind häufiger anzutreffen.

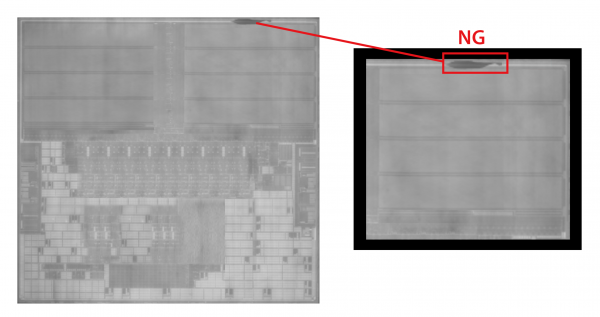

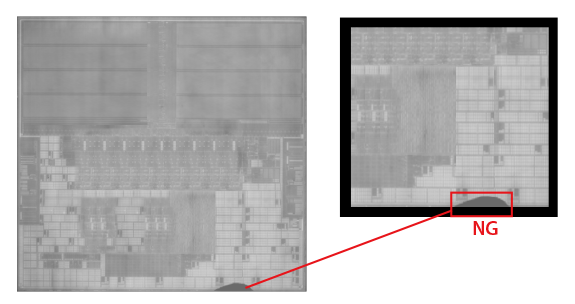

Unvorhersehbarkeit von Rissbildung an den Kanten von Dies

Risse an den Kanten, die während des Wafer-Dicings entstehen, beeinträchtigen die Festigkeit des Wafers. In schweren Fällen kann dies zu Bruch führen, wenn der Chip in nachfolgenden Produktionsprozessen belastet wird. Die Lage, Größe und Form der Risse variieren dabei jedes Mal, und traditionelle optische Inspektionen können solche unvorhersehbaren Fehler nicht genau identifizieren.

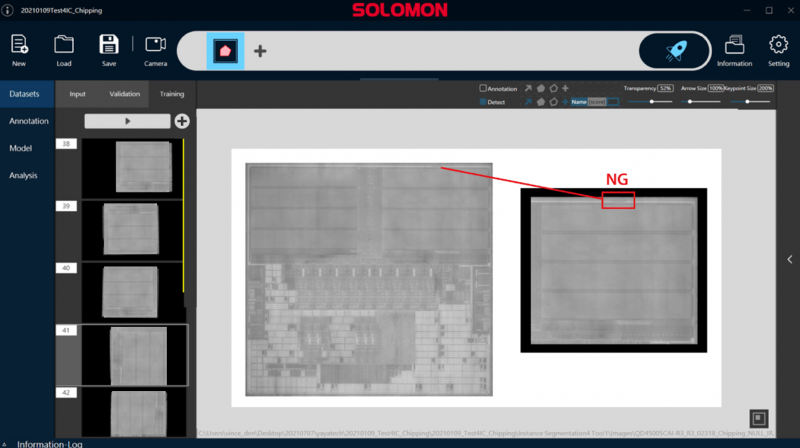

Fundamentlegung für Verpackungen mit KI

Mit überlegenen Erkennungsfähigkeiten kann SolVision ein KI-Modell trainieren, das Wafer inspiziert und Produktionsfehler durch Bildverarbeitung erkennt. Das System ermöglicht die automatische Erkennung und Lokalisierung verschiedener Variationen von abgebrochenen Kanten in Echtzeit, wodurch die Möglichkeit von Bruch in späteren Verpackungsprozessen erheblich reduziert wird.

KI-Inspektion

Rissige Kanten