SolVisionCaso di Studio

Rilevamento di Difetti di Scheggiatura nel Dicing dei Wafer

Controllo qualità dei die semiconduttori con l’AI

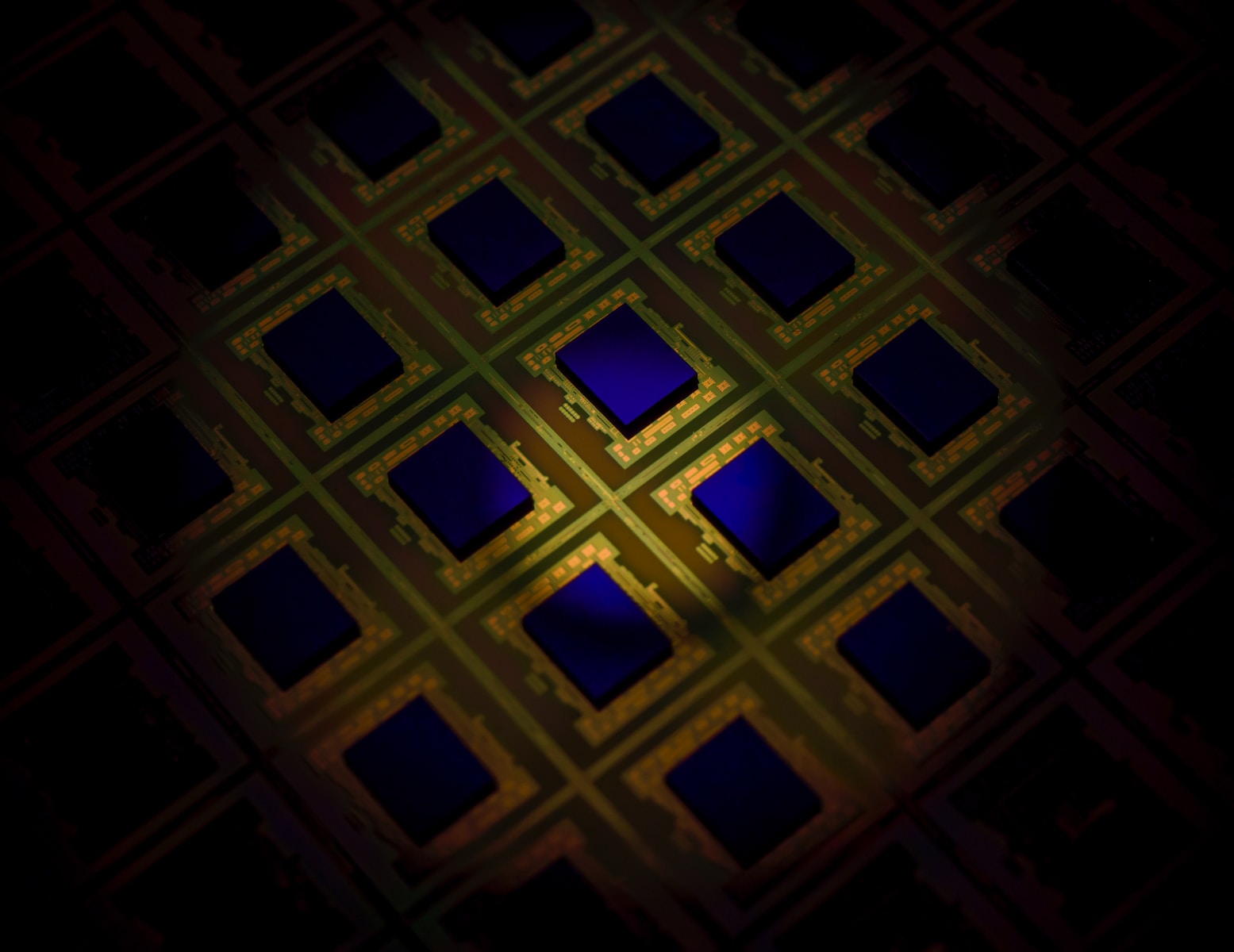

Riduzione delle dimensioni dei wafer semiconduttori

Il taglio dei wafer consente di suddividere il wafer in singoli die per le successive fasi di lavorazione. Poiché l’elettronica moderna richiede wafer più sottili, piccoli e leggeri, i chip più piccoli richiedono processi di taglio più precisi. I percorsi di taglio sono più stretti, i cristalli di silicio diventano più fragili e i danni causati dal taglio sono più frequenti.

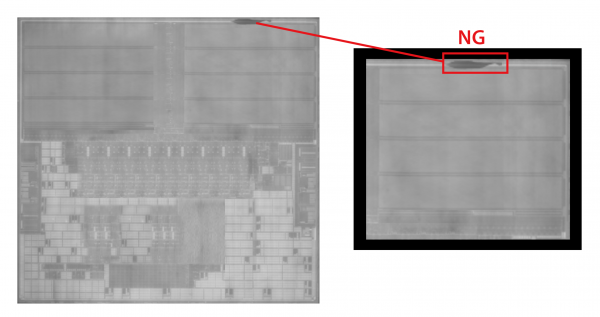

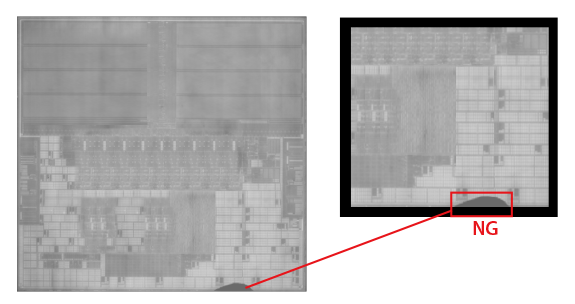

Imprevedibilità delle crepe ai bordi dei die

Le crepe ai bordi causate durante il dicing dei wafer compromettono la resistenza del wafer. Nei casi più gravi, possono provocarne la rottura quando il chip è sottoposto a stress nelle fasi successive della produzione. La posizione, la dimensione e la forma delle crepe variano ogni volta, e l’ispezione ottica tradizionale non è in grado di identificare con precisione questi difetti imprevedibili.

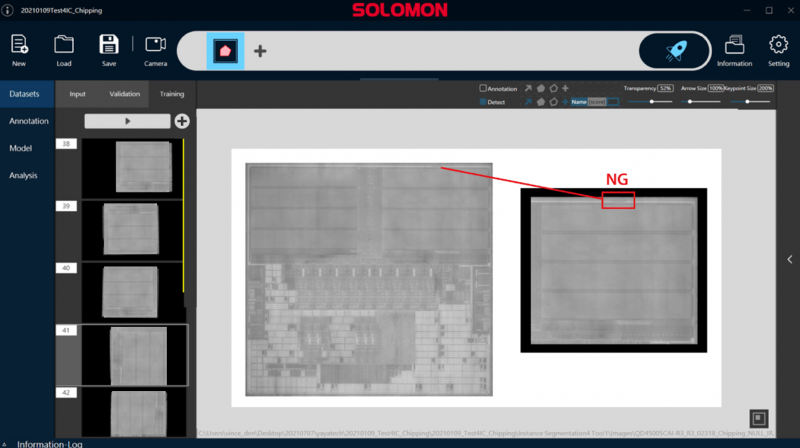

Creare basi solide per il packaging con l’AI

Grazie alle sue avanzate capacità di riconoscimento, SolVision può addestrare un modello AI in grado di ispezionare i wafer e riconoscere i difetti di produzione tramite l’elaborazione delle immagini. Il sistema consente di rilevare automaticamente in tempo reale le diverse varianti di scheggiature ai bordi, riducendo notevolmente il rischio di rottura durante le fasi successive del packaging.

Ispezione AI

Crepe ai bordi