SolVisionFallstudie

KI-Inspektionslösung für Halbleiterwafer

Qualitätskontrolle von chemisch-mechanischen Polierprozessen (CMP)

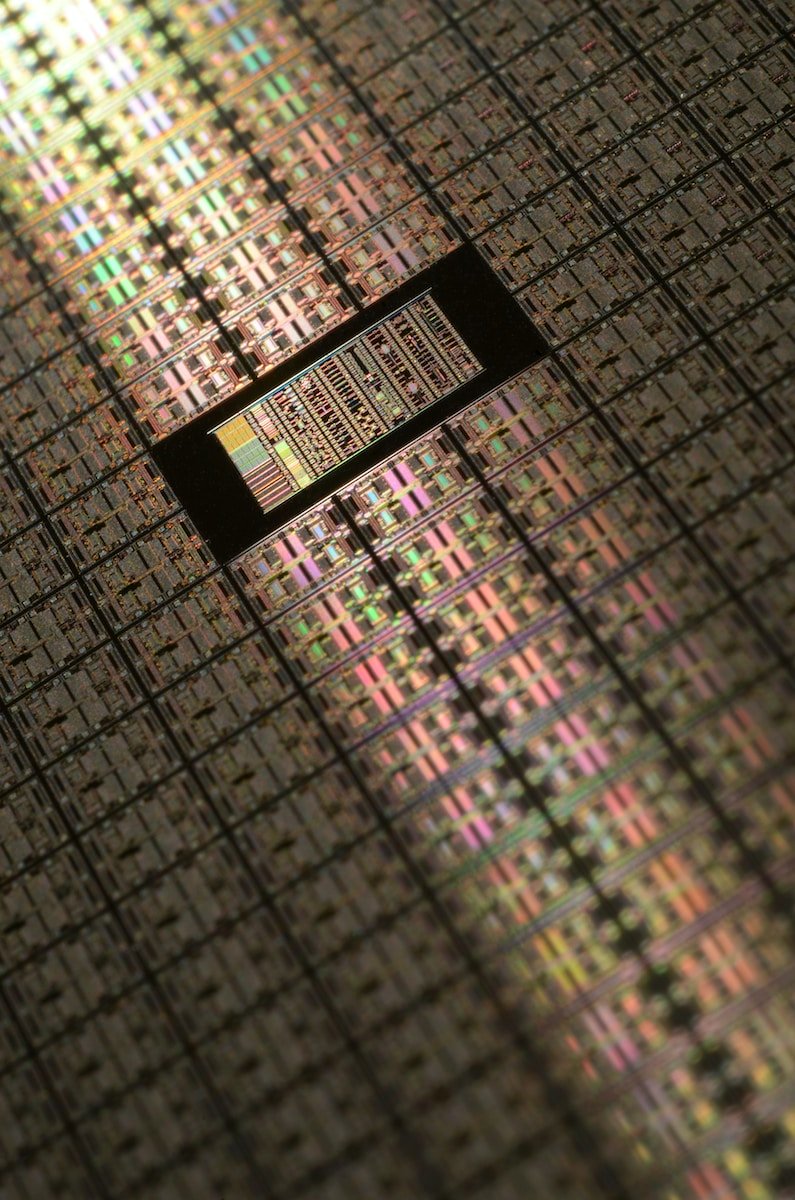

CMP und Wafer-Oberflächen

Die chemisch-mechanische Planarisierung (CMP) ist ein unverzichtbarer Prozess in der Halbleiterfertigung, dessen Zweck darin besteht, kleine Defekte zu beheben, die in vorhergehenden Produktionsschritten entstanden sind. Jede Wafer-Schicht muss poliert und alle überschüssigen Materialien von ihrer Oberfläche durch CMP entfernt werden, bevor die nächste Schicht hergestellt werden kann. Allerdings können übermäßig große Partikel und Abrasionen aus der Schlämme kleine Kratzer auf dem Wafer verursachen, die die häufigste Art von Defekten sind, die durch CMP-Prozesse entstehen.

Komplexe Hintergründe und subtile Wafer-Defekte

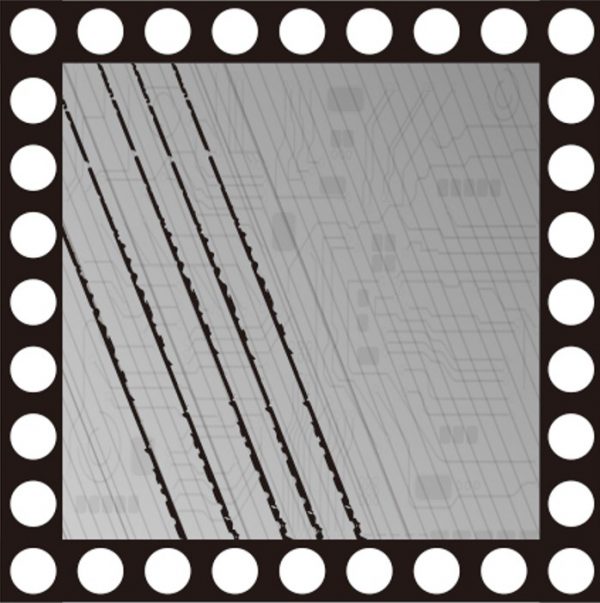

Defekte, die durch CMP verursacht werden, umfassen in der Regel feine Kratzer, Partikelrückstände und Ablagerungen von Polierpads. Nach dem Polieren erzeugt der Wafer extrem flache Polierstreifen, die einen komplexen Hintergrund in den Inspektionsbildern bilden. Da die Arten und Positionen der verschiedenen Defekte nicht festgelegt sind, können sie nicht leicht erkannt werden. Weitere häufige Oberflächendefekte wie weiße Flecken, schwarze Flecken, Wasserflecken und Blasen sind vielfältig und weisen keine unterscheidbaren oder standardisierten Merkmale auf. Die logisch basierten Regeln und Algorithmen traditioneller Systeme sind unzureichend für eine effektive Inspektion eines gesamten Wafers.

KI-gestützte Fehlererkennung

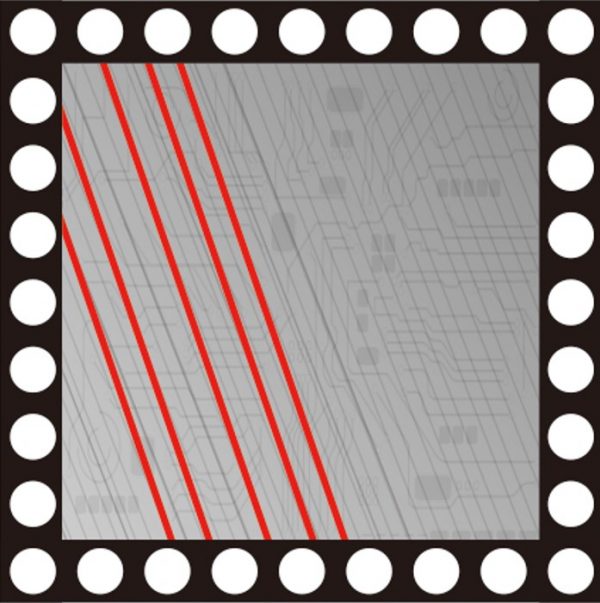

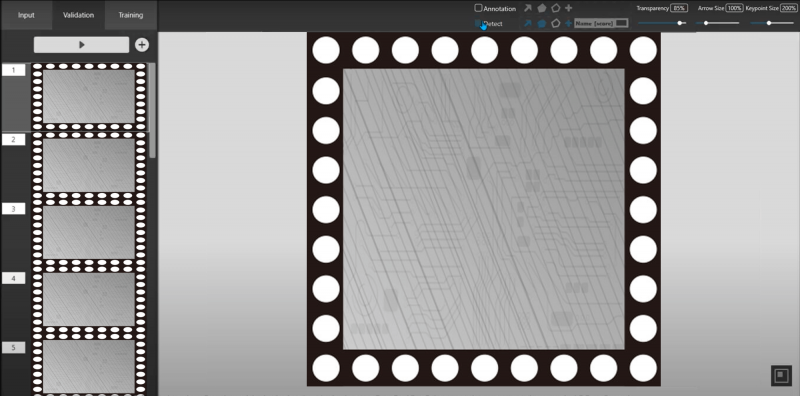

Durch die Verwendung des Segmentierungswerkzeugs von SolVision können winzige Defekte wie feine Kratzer in Musterbildern lokalisiert und markiert werden, um das KI-Modell zu trainieren. Selbst in komplexen oder unruhigen Hintergründen macht SolVision diese obskuren Produktionsfehler und deren Merkmale sichtbar und kann schnell deren Standort und Größe für verbesserte Inspektionen identifizieren.

KI-Inspektion

Kratzer auf der Oberfläche